# Pseudomorphic HEMT Manufacturing Technology for Multifunctional Ka-Band MMIC Applications

C. S. Wu, *Senior Member, IEEE*, C. K. Pao, *Member, IEEE*, W. Yau,

H. Kanber, *Member, IEEE*, M. Hu, S. X. Bar, A. Kurdoghlian,

Z. Bardai, *Member, IEEE*, D. Bosch, C. Seashore, *Member, IEEE*, and M. Gawronski, *Member, IEEE*

**Abstract**—We have demonstrated very good performance, high yield Ka-band multifunctional MMIC results using our recently developed 0.25- $\mu$ m gate length pseudomorphic HEMT (PHEMT) manufacturing technology. Four types of MMIC transceiver components—low noise amplifiers, power amplifiers, mixers, and voltage controlled oscillators—were processed on the same PHEMT wafer, and all were fabricated using a common gate recess process. High performance and high producibility for all four MMIC components was achieved through the optimization of the device epitaxial structure, a process with wide margins for critical process steps and circuit designs that allow for anticipated process variations, resulting in significant performance margins. We obtained excellent results for the Ka-band power amplifier: greater than 26 dBm output power at center frequency with 4.0% standard deviation over the 3-in. wafer, 2-GHz bandwidth, greater than 20 percent power-added efficiency, over 8 dB associated gain, and over 10 dB linear gain. The best performance for the Ka-band LNA was over 17 dB gain and 3.5 dB noise figure at Ka-band. In this paper, we report our device, process, and circuit approach to achieve the state-of-the-art performance and producibility of our MMIC chips.

## I. INTRODUCTION

**G**aAs-BASED pseudomorphic HEMT (PHEMT) has emerged as one of the most important technologies for a variety of advanced microwave and millimeter wave systems. It has been used for multifunctional applications such as high power, high efficiency, and low noise at frequencies ranging from *C*-band up to *W*-band [1]–[13]. Because of its broad applicability to a multitude of system requirements, there is an ever increasing demand for PHEMT-based products. PHEMT manufacturing technology urgently needs to be developed to cope with this increasing demand at microwave and millimeter wave frequencies.

In the past few years, we have worked intensively on the development of advanced PHEMT technology for microwave and millimeter wave applications. To achieve a high-yield, high-performance PHEMT manufacturing technology, we have optimized both the device epitaxial structure and the

Manuscript received December 2, 1993; revised May 2, 1994. This work was supported by Hughes IR&D and the ARPA MIMIC Phase 2 programs.

C. S. Wu, C. K. Pao, W. Yau, H. Kanber, M. Hu, S. X. Bar, A. Kurdoghlian, and Z. Bardai are with Gallium Arsenide Operations, Hughes Aircraft Company, Torrance, CA 90509 USA.

D. Bosch, C. Seashore, and M. Gawronski are with Alliant Techsystems, Hopkins, MN 55343 USA.

IEEE Log Number 9407294.

fabrication process. We have applied manufacturing disciplines to the PHEMT process and as a result have consistently obtained higher yield, producible and uniform PHEMT's. In addition, with our optimized device epitaxial structure, we have demonstrated superior performance Ka-band multifunctional PHEMT MMIC low noise amplifiers (LNA's), power amplifiers (PA's), mixers, and voltage controlled oscillators (VCO's), all fabricated on the same wafer. The best power performance was demonstrated with a balanced amplifier configuration that yielded an output power of 500 mW with 12 dB associated gain and a power-added efficiency of 32% over the 34–36 GHz frequency range [12]. Low noise amplifiers with a noise figure of 3.5 dB with an associated gain of 17 dB over the 33–37 GHz frequency range have also been demonstrated. Multiple function PHEMT MMIC's on the same wafers have also been successfully fabricated on the ARPA MIMIC Phase 2 program [14].

In this paper, we will present our device epitaxial design, device fabrication process, and MMIC design approach used to achieve these high yield, multifunctional Ka-band PHEMT MMIC's. We also present our wafer lot data in terms of performance, uniformity, and wafer-to-wafer producibility.

## II. APPROACH

Three key areas were optimized to achieve the results presented in this paper: 1) a PHEMT epitaxial structure that would be process tolerant and yet yield high performance for multiple MIMIC circuit functions; 2) a PHEMT process with broad process margin; and 3) a process tolerant circuit design. We will discuss these in detail in the following sections.

### A. PHEMT Epitaxial Design Optimization

Proper PHEMT epitaxial structure design is essential to simultaneously achieve processing margins, particularly for the gate recess process and state of the art device performance. To achieve this we have focused on two critical areas—design and optimization of the GaAs cap layer and the Si planar doping layer. In addition, to obtain the required low phase noise at low frequency for both mixer and oscillator applications, we have utilized low Al content 24%, potentially DX-center-free AlGaAs layers in the device epitaxial structure. We will discuss PHEMT epitaxial design considerations for both mixer and oscillator applications later on this paper.

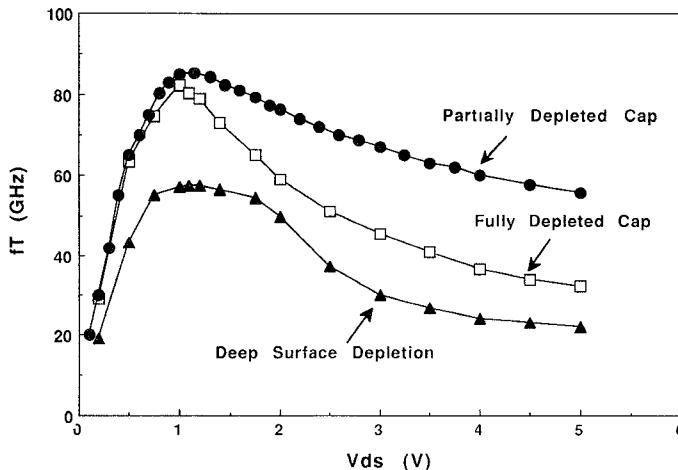

Fig. 1. Cutoff frequency ( $f_T$ ) as a function of  $V_{ds}$  for double-sided doped PHEMT devices having various cap structures. The partially depleted cap structure exhibits relatively flat high  $f_T$  values in a broad  $V_{ds}$  range, desired for multifunctional applications. Note that the total gatewidth of measured devices is 200–300  $\mu\text{m}$ .

#### A. Cap Layer Design

Cap layer design is critical to PHEMT device yield and performance. We have observed that a thin cap layer can lead to high device yield and uniformity. By reducing the thickness of cap layer from 500  $\text{\AA}$  to 300  $\text{\AA}$ , both yield and uniformity can be improved by 20–30%. This improvement is the result of a reduction in the variation of gate recess etch depth as the cap layer thickness is decreased. However, the cap layer cannot be too thin (or have too little charge), otherwise it will lead to degradation of device characteristics. A depleted cap layer can lead to a drastic degradation of unity current gain cutoff frequency ( $f_T$ ), particularly at high drain-source voltage ( $V_{ds}$ ) ranges. Fig. 1 shows  $f_T$  as a function of  $V_{ds}$  for various cap structures.  $f_T$  remains relatively flat for a partially depleted cap structure, which is desired for all high frequency applications such as power and low noise. On the other hand, the conducting cap (filled with excessive charge) can result in a low breakdown voltage for PHEMT devices because of electric field crowding on the drain side adjacent to the gate fingers. Through judicious selection of the cap layers we have achieved desired saturation current ( $I_{sat}$ ) values, measured as the current from both cap and channel layers, which also yield high  $f_T$  and high breakdown voltage ( $8 \text{ V} < BV_{ds} < 9 \text{ V}$ ) for millimeter wave applications. This has led to high circuit performance for our multifunctional Ka-band MMIC circuits fabricated on the same wafer.

*Si Planar Doping Structure Design:* A key focus for our effort was the optimization of the spacer layer thickness and doping concentrations for the Si planar doping layer(s) in the PHEMT structure. The criteria here was to achieve high channel charge density and high carrier mobility. In addition, we evaluated the yield and performance for both single- and double-sided delta-doped structures. We observed that double-sided doped devices exhibit relatively higher noise figure (about 0.1–0.2 dB higher) than single-sided doped devices. This is believed to be due to relatively low carrier mobility often obtained from the double-sided doped structures. In the double-sided doped structure, the reduced carrier mobility can

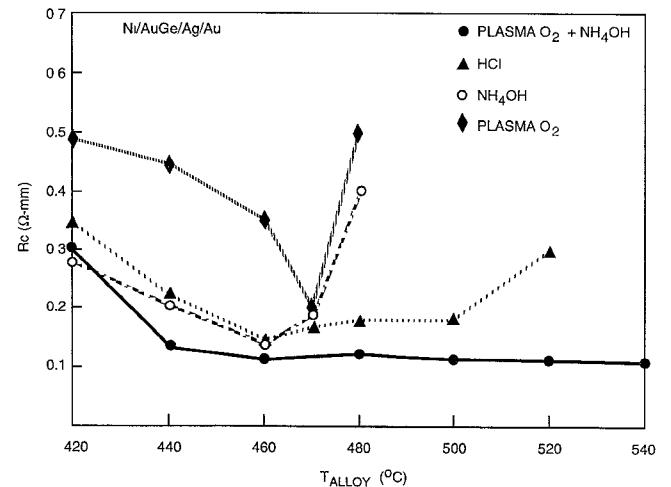

Fig. 2. Contact resistance ( $R_c$ ) as a function of alloying temperature for Ag barrier ohmic samples using different pre-metal deposition cleaning procedures. The data shows the strong effects of the cleaning procedure on the contact alloying stability and suggests the  $O_2$  plasma +  $NH_4OH$  process leads to the cleanest surface and thus a broad optimal temperature range for low  $R_c$ .

be attributed to the incorporation of Si atoms into InGaAs channel layer from the bottom Si doping layer. In our process, the single-sided delta doped devices exhibited lower yield, poorer uniformity, and lower power characteristics than the double-sided delta-doped devices, despite having lower noise figures. We have attributed the improvement of both device yield and uniformity of the double sided delta doped structure to their relative insensitivity to the variation in the gate recess depth. In terms of power performance, due to their limited channel charge the single-sided doped devices did not generate as much power as the double-sided doped devices.

*PHEMT Epitaxial Design Consideration for Mixer and Oscillator Applications:* Both mixer and oscillator circuits require high cutoff frequency, high gain, and low noise characteristics. These requirements are the same as for the low noise and power PHEMT amplifiers at Ka-band frequencies. Both of these circuits, however, also require active devices with low phase noise at lower frequencies in order to obtain high spectral purity. AlGaAs layers in the PHEMT structure are used as both a Schottky contact layer and a buffer layer. It is well known that the Si-doped AlGaAs layer is filled with high density of electrically active DX-centers if the Al/Ga ratio is higher than a threshold value of 25%. Note that the DX-centers are electrically deep levels and act as generation-recombination (g-r) centers. They can produce g-r noise and thus low frequency phase noise. The density of these electrically active DX-centers is reduced significantly as the Al content in AlGaAs falls below 25%. Therefore, low Al content in AlGaAs is desired for low phase noise. However, low Al content can lead to poor charge transfer to InGaAs channel layer and thus degrade gain and power characteristics. A 24% Al content in double-sided doped AlGaAs layers and 20% In content in InGaAs channel layer results in channel charge density of  $3.2 \pm 0.2 \times 10^{12} \text{ cm}^{-2}$ , an excellent compromise for the selected applications here.

An Al content of 24% was selected based on the above considerations. This has resulted in low phase noise performance

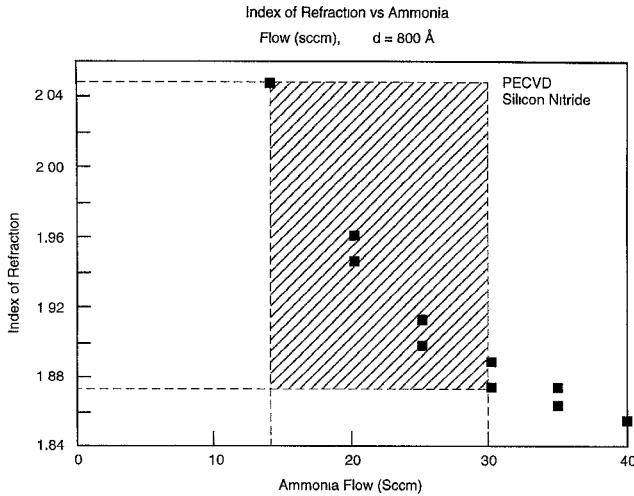

Fig. 3. Index of refraction ( $n$ ) of the silicon nitride film as a function of ammonia flow rate during the film preparation in the plasma enhanced  $C_{VD}$  (PECVD) chamber. We observed that our PHEMT devices exhibited a minimal change in breakdown voltage and other dc characteristics after passivation with PECVD silicon nitride film, deposited at various ammonia flow rate from 14 to 30 sccm. The area within the dotted lines shows the acceptable region of ammonia flow rate and measured refractive index.

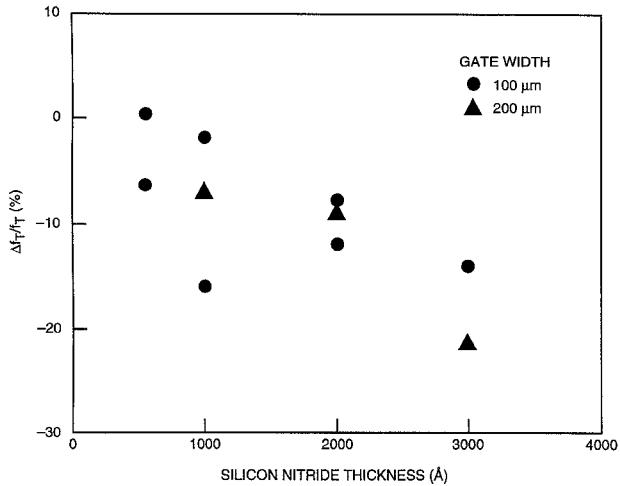

Fig. 4. Reduction in cutoff frequency ( $f_T$ ) as a function of silicon nitride thickness for PHEMT devices after passivation. A 2000- $\mu$ m silicon nitride passivation can result in 10–15% reduction in  $f_T$ .

for the mixer and oscillator. Note that in contrast to PHEMT, lattice-matched AlGaAs/GaAs HEMT requires high Al content in AlGaAs layers in order to achieve the same level of conduction band discontinuity, channel charge concentration, and charge confinement. As a result of the higher Al content used, AlGaAs/GaAs HEMT's, often exhibits higher phase noise than PHEMT's. Recently, R. Plana *et al.* [15] have reported that PHEMT's exhibit better low frequency noise than FET's and conventional HEMT's. This preliminary result indicates that PHEMT may be suitable for lower frequency low phase noise applications, in addition to the millimeter wave low noise and power applications.

#### B. Manufacturable PHEMT Process Development

Broad process margin is key to a high yield manufacturing process. In the PHEMT process development, we have

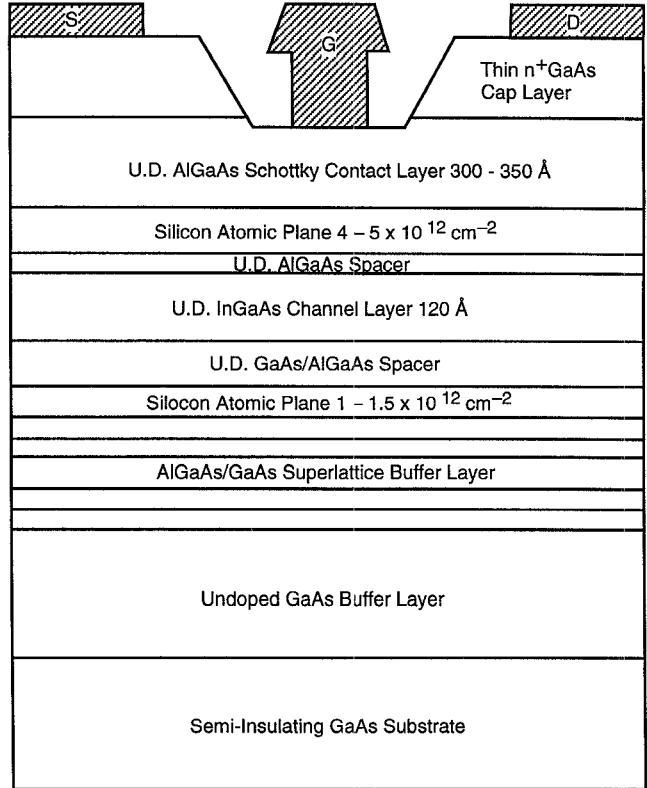

Fig. 5. Our baseline, thin cap, double-sided doped PHEMT structure. The cap layer of the structure is partially depleted. Using a single-gate recess process, devices fabricated on this structure have demonstrated multifunctional Ka-band MMIC performance.

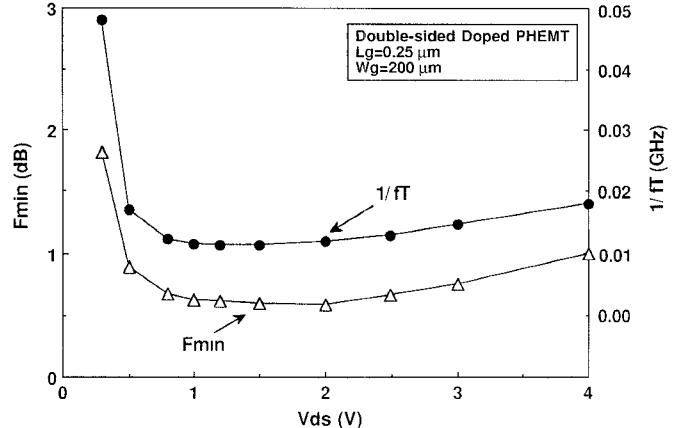

Fig. 6. Minimum noise figure ( $F_{min}$ ) at 10 GHz and  $1/f_T$  as a function of  $V_{ds}$  for our baseline PHEMT devices.  $F_{min}$  values are low (0.6–1.0 dB) in a broad  $V_{ds}$  range (0.5–4 V).  $F_{min}$  shows a close correlation with  $1/f_T$ .

optimized several critical process steps. We present two key studies and their results in the following sections.

**Ohmic Contact Process:** We extensively studied the Ag barrier ohmic metal contacts for PHEMT. Our results indicate a strong dependence of ohmic contact characteristics on the pre-metal-deposition cleaning procedure. As shown in Fig. 2, the ohmic sample pre-cleaned with combined a  $O_2$  plasma and  $NH_4OH$  process exhibited a very broad optimal alloy temperature window ( $440^\circ C$ – $540^\circ C$ ), outperforming other samples cleaned by other techniques [16]. This suggests a noncritical alloy process for our optimized ohmic contact process.

$$W_g = 4 \times 50 \mu\text{m}, V_{ds} = 3\text{V}, V_{gs} = -0.99 \text{V}, I_{ds} = 25 \text{mA}$$

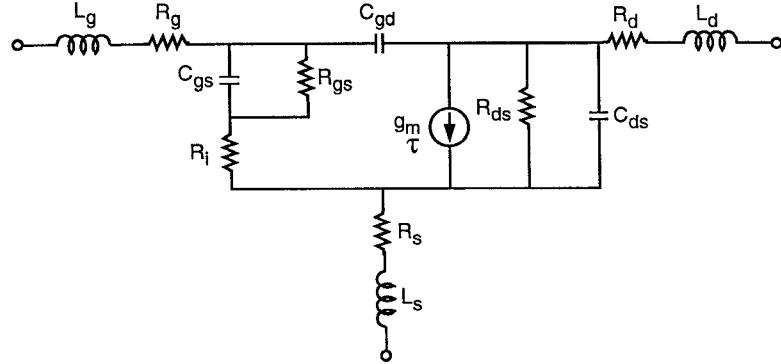

| $g_m$<br>(mS) | $C_{gs}$<br>(fF) | $C_{gd}$<br>(fF) | $C_{ds}$<br>(fF) | $\tau$<br>(ps) | $R_g$<br>( $\Omega$ ) | $R_{gs}$<br>( $\text{K}\Omega$ ) | $R_I$<br>( $\Omega$ ) | $R_s$<br>( $\Omega$ ) | $R_{ds}$<br>( $\Omega$ ) | $R_d$<br>( $\Omega$ ) | $L_g$<br>(pH) | $L_s$<br>(pH) | $L_d$<br>(pH) | $f_T$<br>(GHz) |

|---------------|------------------|------------------|------------------|----------------|-----------------------|----------------------------------|-----------------------|-----------------------|--------------------------|-----------------------|---------------|---------------|---------------|----------------|

| 110.0         | 231.6            | 46.0             | 73.2             | 0.41           | 1.29                  | 3.41                             | 1.85                  | 1.8                   | 158.0                    | 8.59                  | 34.8          | 1.3           | 25.0          | 64.8           |

Fig. 7. Equivalent circuit element values for our devices ( $L_g = 0.25 \mu\text{m}$ ,  $W_g = 4 \times 50 \mu\text{m}$ ).

**Silicon Nitride Passivation:** We found that the PHEMT devices exhibited a minimal change in breakdown voltage and other dc characteristics after passivation with plasma enhanced chemical vapor deposited (PECVD) silicon nitride film, deposited at various ammonia flow rates from 14 to 30 sccm. Fig. 3 shows the relation between ammonia flow rate and measured refractive index of the deposited silicon nitride. The area within the dotted lines show an acceptable region of ammonia flow rate and measured refractive index, where the PHEMT devices exhibited less than 0.5 V change in breakdown voltage after passivation. This suggests a broad deposition process margin for our silicon nitride as a passivation layer for PHEMT devices.

However, as other researchers have reported, we observed a degradation of  $f_T$  by 10–15% for the PHEMT devices for silicon nitride passivation thicknesses beyond 2000 Å, as shown in Fig. 4. The exact causes of this degradation are complex and are still under investigation. But it is certain that part of the degradation is due to the increase in gate capacitance in response to the presence of high dielectric constant silicon nitride surrounding the gate finger region. Nevertheless, we have controlled the run-to-run variation of  $f_T$  after passivation within  $\pm 7\%$  for the 0.25- $\mu\text{m}$  PHEMT devices.

### III. DEVICE AND MMIC FABRICATION

The device epitaxial structure utilized in this work is a double-sided delta-doped AlGaAs-InGaAs-GaAs PHEMT shown in Fig. 5. The structure was grown by MBE on a semi-insulating GaAs substrate. Typical values obtained from Hall measurement for the InGaAs channel sheet charge density and room temperature carrier mobility are  $3.2 \pm 0.2 \times 10^{12} \text{ cm}^{-2}$  and  $5300\text{--}5600 \text{ cm}^2/\text{V}\cdot\text{sec}$ , respectively. The gate contact AlGaAs layer was undoped so that a suitably high gate-drain breakdown voltage can be achieved.

We etched a mesa structure for device isolation and utilized low contact resistance AuGe-based alloyed ohmic contacts for both the source and drain. We employed low-resistance mushroom gates. The gates were defined in PMMA/PMAA bilayer resist by e-beam lithography using a Philips Beamwriter machine. The gate length is 0.25  $\mu\text{m}$ . After gate recess etching, a Ti-Pt-Au metal system was evaporated onto the gate opening region and lifted off to form gate fingers.

Other MMIC components fabricated include TaN resistors, Ti-Au transmission lines, dielectric capacitors, and Au-plated airbridges. After completing front-side processing, thinned the substrate to 4 mils, etched via holes and metallized the backside with Au. The device results reported here come from several different PHEMT wafers. The MMIC results presented in this paper were measured on two device lots, each containing four PHEMT wafers with the above structure.

### IV. DEVICE PERIPHERIES

To simplify device characterization, we employ devices with only 50- and 75- $\mu\text{m}$  unit gate fingers. For example, a 100- $\mu\text{m}$  FET in the low noise amplifier consists of two gate fingers each with a 50  $\mu\text{m}$  width, while a 450- $\mu\text{m}$  FET in the power amplifier employs six 75- $\mu\text{m}$  unit gate fingers. This arrangement allows for easier device scaling and FET model verification. Typical dc bias conditions for these FETs are 25%  $I_{dss}$  and 50%  $I_{dss}$  for low noise and power operation, respectively.

### V. DEVICE RESULTS

The fabricated PHEMT's typically exhibited a full-channel drain current density ( $I_{\max}$ ) of over 600 mA/mm and a peak transconductance ( $g_m$ ) of 400–450 mS/mm. The source-drain breakdown voltage ( $BV_{ds}$ ) was 8–9 V and pinch off voltage ( $V_{po}$ ) was  $-1.1 \text{V}$ . The power device ( $< 400 \mu\text{m}$ ) typically exhibited output power density of 700–800 mW/mm with

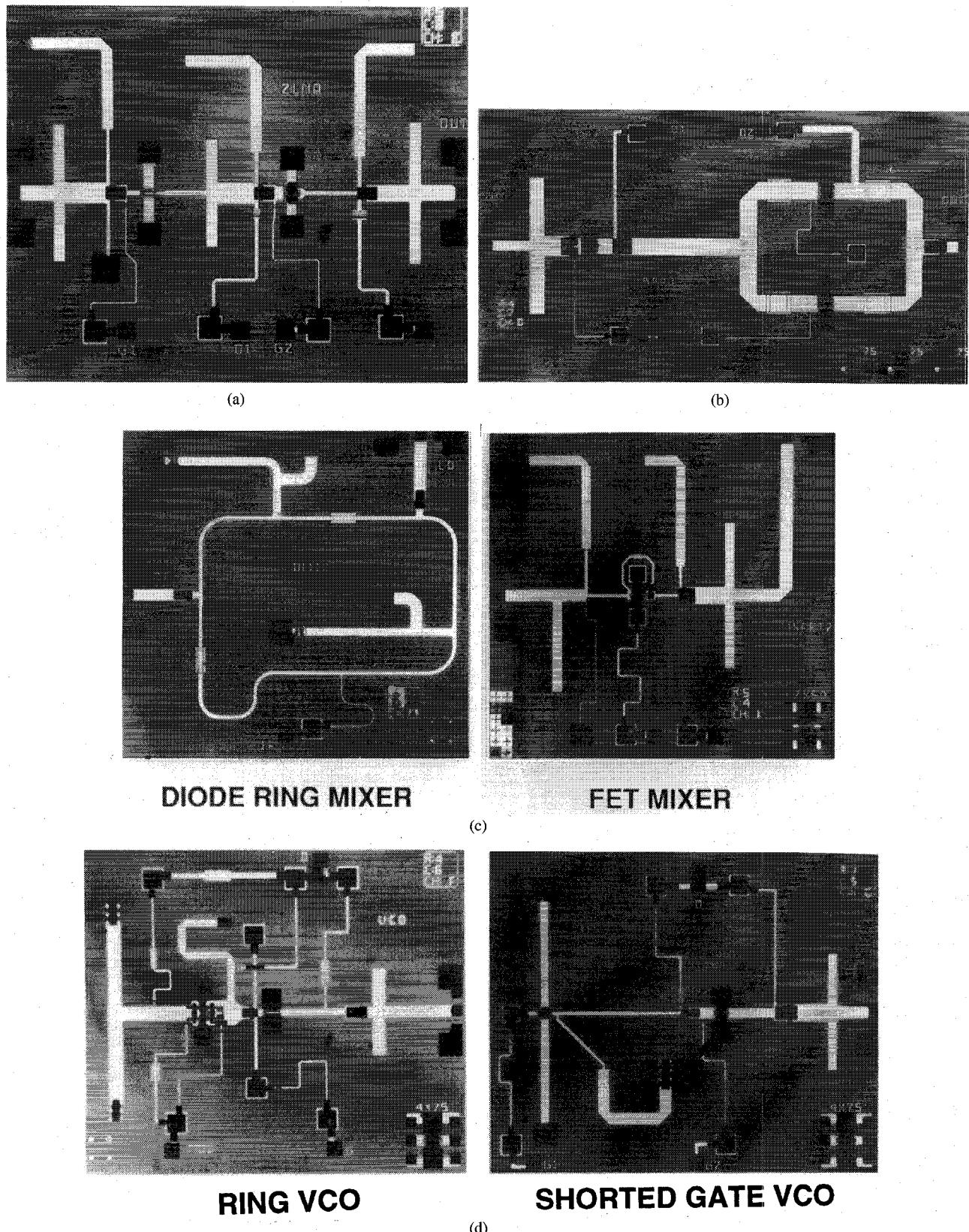

Fig. 8. (a) Two-stage PHEMT Ka-band MMIC low noise amplifier. Chip size is  $1.875 \times 2.25$  mm. (b) PHEMT Ka-band MMIC balanced power amplifier. Chip size is  $1.875 \times 3.25$  mm. (c) PHEMT Ka-band diode ring and FET mixers. Individual chip size is  $1.875 \times 2.00$  mm. (d) PHEMT Ka-band ring and shorted-gate voltage controlled oscillators ( $V_{CO}$ ). Individual chip size is  $1.875 \times 2.25$  mm.

power-added efficiency of 35–40%. A typical  $100\text{-}\mu\text{m}$  device biased at  $25\%I_{dss}$  exhibited a noise figure of approximately

0.6 dB at 10 GHz and 1.2 dB at 18 GHz. Fig. 6 shows the device  $F_{min}$  versus  $V_{ds}$ . Because of the relative insensitivity

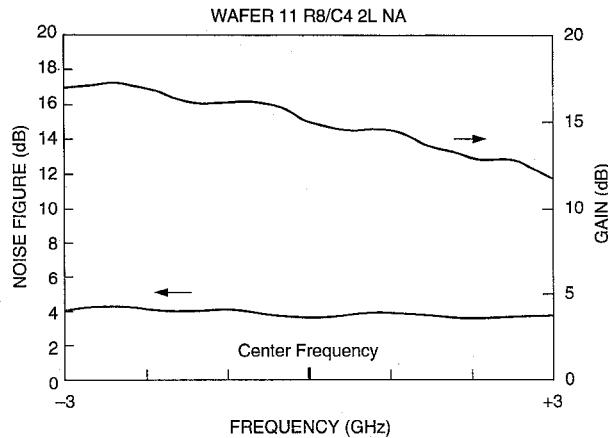

Fig. 9. The performance of both noise figure and gain in Ka-band range for our 2-stage LNA. The LNA exhibits a noise figure between 3.5 and 5.0 dB, across the 5-GHz bandwidth.

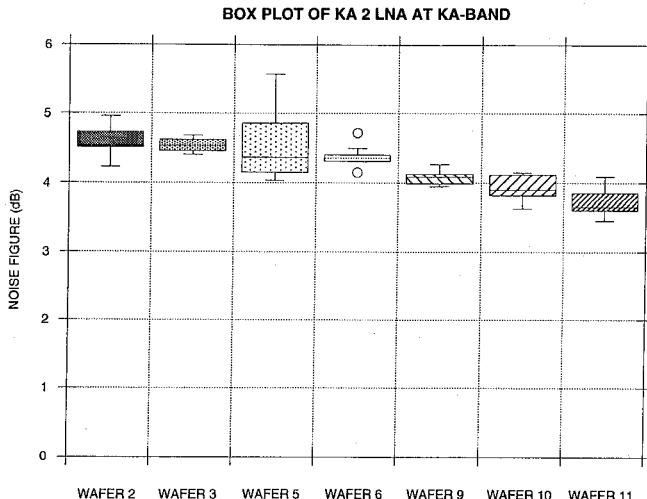

Fig. 10. Noise performance of LNA's from seven wafers tested. The noise performance distribution was uniform from wafer to wafer. The improvement of noise performance for the later three wafers is due to circuit redesign.

of  $f_T$  to variations in  $V_{ds}$  and low gate leakage, the optimized double-sided doped structure showed a broad low  $F_{min}$  range. In addition, the devices exhibited a relatively broad low  $F_{min}$  range as a function of  $I_{ds}$  as a result of slowly varying  $g_m$  and  $f_T$ . Both are desired characteristics for low noise amplifier designs.

We have consistently achieved high yield, high producibility, and high uniformity device results using the above manufacturable processes and designs. We have recently repeated our results on the PHEMT wafer lots fabricated for the MIMIC Phase 2 program. The wafers exhibited uniform values of both  $I_{dss}$  (at  $V_g = 0$  V) and  $V_{po}$  with only 13% deviation across the 3-in. wafers. Wafer-to-wafer uniformity is excellent:  $I_{dss}$  is  $360 \pm 1.7$  mA/mm, and  $V_{po}$  is  $-1.09 \pm 0.04$  V for a 4-wafer lot. In addition, the  $f_T$  values are tightly grouped at  $61.32 \pm 2.45$  GHz across a 3-in. wafer measured at  $V_{ds}$  of 3 V. Fig. 7 shows typical extracted circuit element values for our devices.

## VI. MMIC CIRCUIT TECHNOLOGY

Four major Ka-band MMIC transceiver components were designed and fabricated to demonstrate the feasibility of our

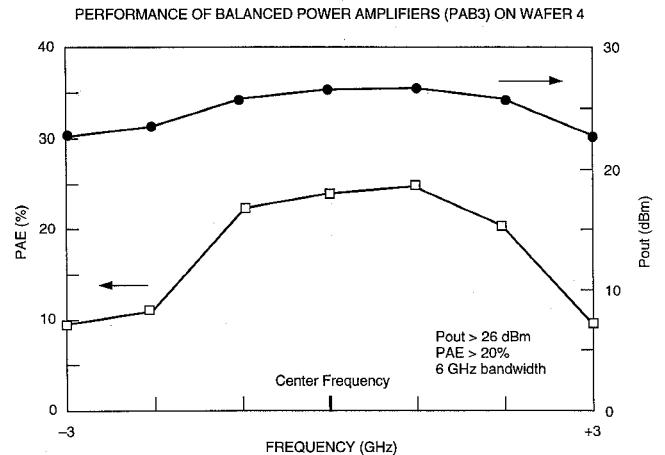

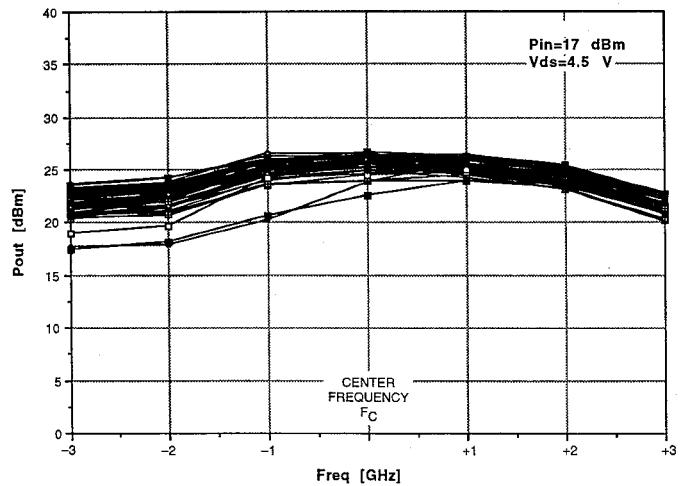

Fig. 11. Typical output power characteristics of our Ka-band balanced power amplifiers.

Fig. 12. Ka-band power amplifier power performance on a 3-in. PHEMT wafer. The power output of 49 MMIC's is shown on this wafer.

PHEMT manufacturing technology. As mentioned previously, the circuits are low noise amplifiers, power amplifiers, mixers, and voltage-controlled oscillators. The circuits were designed to achieve high performance with these goals in mind: high yield, good uniformity, and producibility. A rapidly maturing fabrication technology and advances in microwave CAD tools have allowed circuit design at Ka-band to be much more straightforward. Designing a millimeter-wave circuit that is insensitive to process variation, however, is still an area that needs considerable work. A 14-element equivalent circuit model is typically employed in circuit design. A device model with physical representation can often be used to compare process variations from lot to lot. The proper matching circuit topology is important since it can minimize circuit performance variation. Fig. 8(a)–(d) shows photographs of the Ka-band circuits fabricated on 3-in. PHEMT wafers.

### A. Low-Noise Amplifier

The two-stage low noise amplifier consists of two single-ended stages cascaded in series. A  $100\text{-}\mu\text{m}$  device was employed in the first stage to drive a  $200\text{-}\mu\text{m}$  device in the second stage. The input matching circuit of the LNA was designed for optimum noise performance, while maintaining a good input

Fig. 13. RF power output wafer map of a Ka-band PHEMT wafer. Average output power is 25.4 dB with 4% uniformity over the wafer.

return loss. The second stage amplifier was designed to provide high gain. On-wafer *S*-parameters measured up to 40 GHz and noise parameters characterized up to 18 GHz were utilized in the design.

#### B. Power Amplifier

The power amplifier employs a 300- $\mu$ m device in the first stage to drive a set of two 450- $\mu$ m FET's in the output stage. The circuit consists of mainly microstrip transmission lines which have the advantage of 1) reduced uncertainty in passive element circuit models and 2) reduced coupling between circuit elements. The input matching circuit consists of open circuit stubs and the output matching circuit consists of microstrip transmission lines that serve as an impedance transformer. Both interstage and output matching circuits were designed using a load line technique. The dc bias line was designed using quarter-wavelength transmission lines that present an open circuit to the matching network at the designed frequency, eliminating loading effects.

#### C. Mixers

Two types of mixers were designed: FET mixer and diode mixer.

**FET Mixer:** A FET mixer was designed utilizing the time varying channel resistance of a HEMT device in the linear region. A LO signal, pumping at the gate port, modulates the channel resistance to create frequency mixing with a RF signal coupled to the drain. An IF output is obtained at the source. The conversion loss of the FET mixer is determined by the on and off ratio of the channel resistance, therefore the performance is less sensitive to process variations. Input matching circuit was designed based on the small signal equivalent circuit model, and the output-matching circuit was designed using the effective channel resistance under LO drive. A transmission line is connected between the drain and gate ports to provide parallel resonance with the drain to gate capacitance  $C_{dg}$ . This minimizes the LO signal coupling to the drain port, greatly improving the gate to drain isolation. The IF frequency is so low that the matching circuit is not critical.

Fig. 14. Comparison of conversion loss for both FET and diode mixers at various LO powers.

**Diode Mixer:** A 180-degree rat-race circuit is employed in the diode mixer to drive a pair of diodes 180 degrees out of phase. It then recombines maximally in phase at the IF frequency. Since the mixer operates on the diode's on and off states, the conversion loss is more sensitive to process variations. It also requires a high LO signal to drive the mixer.

#### D. Voltage-Controlled Oscillators (VCO's)

Two types of VCO circuits were designed: a ring VCO and a shorted gate VCO.

**Ring VCO:** The ring VCO was designed by utilizing an active device as a feedback element to form a ring-type oscillator. The matching circuit was designed to maximize the negative resistance at the drain. A buffer amplifier at the oscillator output port, was employed to boost the output power and minimize frequency pulling due to external loading.

**Shorted Gate VCO:** A 100- $\mu$ m PHEMT device was used in a common source configuration to realize a shorted gate oscillator. This design was used to obtain better phase noise at the expense of reducing the tuning bandwidth. As with the ring VCO, the shorted gate VCO utilized a buffer amplifier to boost the output power and minimize frequency pulling.

Fig. 15. Wafer map of conversion loss of FET mixers.

## VII. MMIC MEASUREMENTS AND RF RESULTS

We performed 100% on-wafer measurements for the power amplifiers, diode mixers, FET mixers, LNA's and the oscillator circuits. It should be noted that all measurements were carried out at a constant bias, i.e. the circuits were biased at a constant voltage and current, as opposed to individual bias tuning for each circuit, as reported in some previous publications.

The two-stage LNA exhibited a noise figure between 3.5 and 5.0 dB, across the 5-GHz bandwidth around center frequency at Ka-band. The gain performance of the LNA is as high as 17 dB at 33 GHz, as shown in Fig. 9. The noise performance distribution was uniform from wafer to wafer (the noise performance of seven wafers is shown in Fig. 10, measured at nine test sites on each wafer). The LNA circuit was redesigned and improved for wafers 6–11, and this resulted in lower noise figures (as low as 3.5 dB on wafer 11).

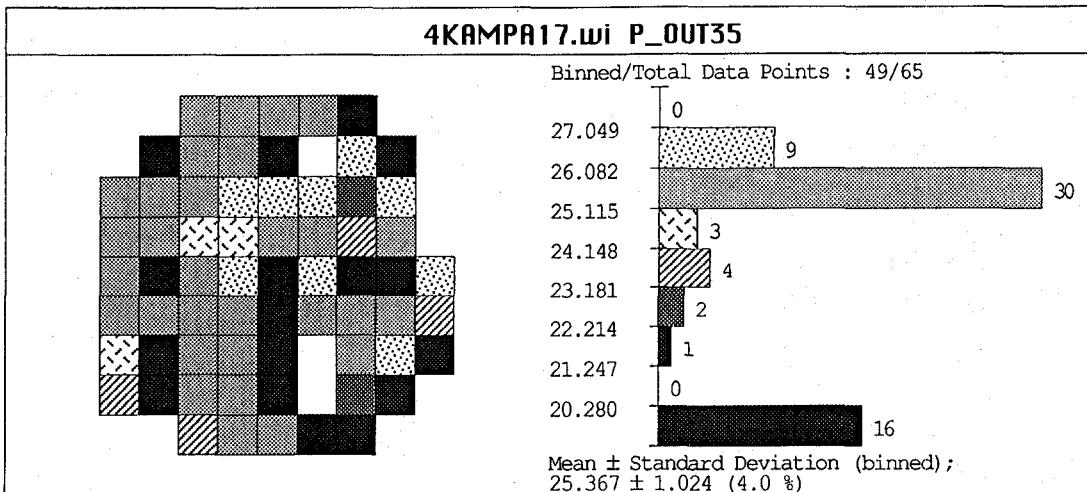

The power amplifiers were measured under both small and large signal conditions. Excellent performance was obtained at Ka-band: an output power of over 26 dBm and a power-added efficiency exceeding 20% were achieved with an associated gain of over 9 dB. Fig. 11 shows output power characteristics of a typical PHEMT wafer, measured across a 6-GHz bandwidth in Ka-band, with 17-dBm input power. A composite plot of 49 2-stage power amplifiers is shown in Fig. 12, exhibiting a tight distribution. Fig. 13 shows output power uniformity for the power amplifiers, with an average output power of 25.37 dBm and a standard deviation of 4% measured at 35 GHz. The tight distribution is shown in the histogram shown on the right side of the figure. There are 9 test reticles and 2 dropouts among the 21 data points that are excluded from the mean output power calculation.

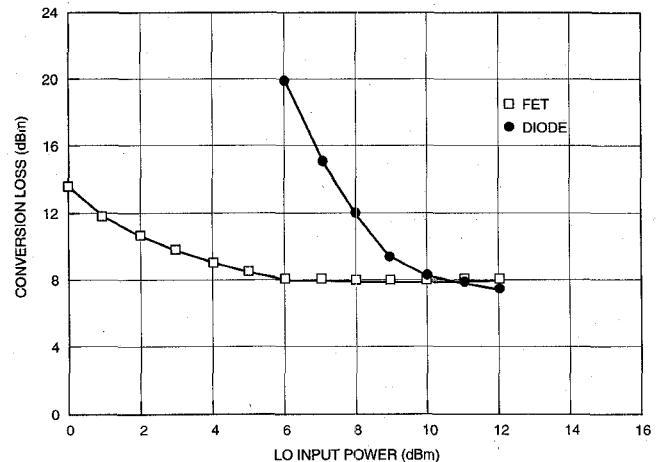

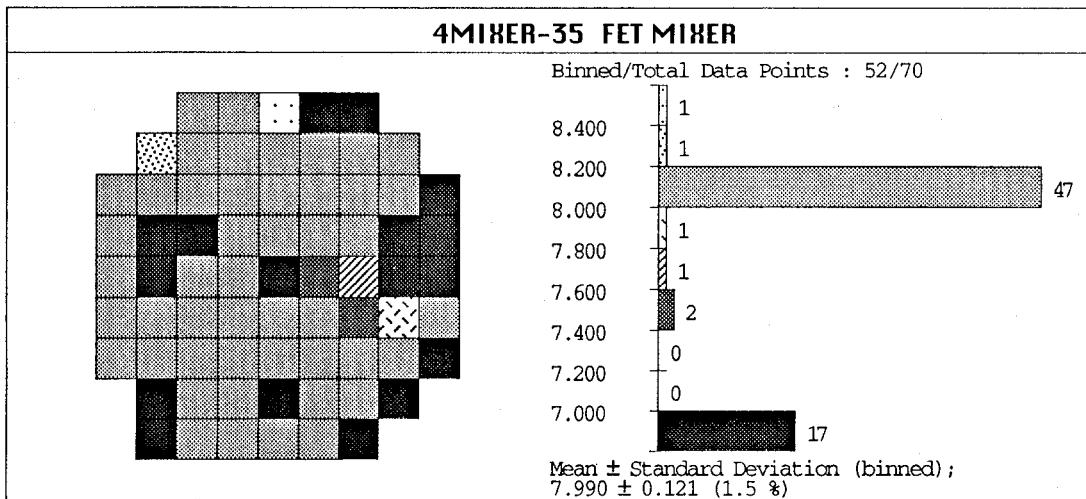

Both FET and diode mixers were measured with 10 dBm LO input power and -5 dBm RF input power at the center of the frequency band. Fig. 14 shows the conversion loss of a typical FET mixer compared with a diode mixer at various LO powers. Both mixers achieved a conversion loss of 7.8 dB at around 10 dBm LO drive. However, a FET mixer requires a much lower LO power to operate. A wafer map of FET mixer conversion loss is shown in Fig. 15. Excellent uniformity was

obtained with an average conversion loss of 8.0 dB and a standard deviation of 2%. The average diode mixer conversion loss is 8 dB with a standard deviation of 4%. The FET mixer exhibits superior uniformity as compared with diode mixers due to the mixing mechanism as described in the previous section. The best wafer exhibited an average conversion loss of 6.55 dB for FET mixers and 7.14 dB for diode mixers.

We also tested two types of VCO's fabricated on the same PHEMT wafers. On one wafer, the average output power was  $15.8 \pm 1.0$  dBm for the ring VCO and  $11.5 \pm 1.5$  dBm for the shorted gate VCO. The phase noise is about -85 dBc/Hz for ring VCO and -90 dBc/Hz at 1 MHz away from the center frequency.

The above results demonstrate that we have obtained state-of-the-art multifunctional performance from these PHEMT wafers, using four types of circuits fabricated on the same wafer.

## VIII. CONCLUSION

We have demonstrated the feasibility of PHEMT manufacturing technology. Multiple circuit performance was measured across the entire wafer under fixed bias conditions, with no attempt to optimize performance of each chip by adjusting its dc bias individually, as opposed to others reporting one of a type of performance based on individual circuit optimization.

To the best of our knowledge, this is the first paper to report truly multifunctional PHEMT circuits with uniform RF performance on the same wafer at millimeter wave frequencies.

## ACKNOWLEDGMENT

The authors would like to thank Drs. D. C. Wang, C. P. Wen, and T. A. Midford from Hughes Aircraft Company and Mr. S. Kiss from the U.S. Air Force for their technical guidance and support. They would also like to thank A. M. Gomez, M. J. Circle, R. D. Larson, and A. Grohs for their process assistance.

## REFERENCES

- [1] H. Q. Tserng, B. Kim, P. Saunier, H. D. Shih, and M. A. Khatibzadeh, "Millimeter-wave power transistors and circuits," *Microwave J.*, pp. 125–135, Apr. 1989.

- [2] P. M. Smith, P. C. Chao, L. F. Lester, R. P. Smith, B. R. Lee, D. W. Ferguson, A. A. Jabra, J. M. Ballingall, and K. H. G. Duh, "InGaAs pseudomorphic HEMTs for millimeter wave power applications," *IEEE MTT-S Dig.*, pp. 927-930, 1988.

- [3] P. M. Smith, M. Y. Kao, P. Ho, P. C. Chao, K. H. G. Duh, A. A. Jabra, R. P. Smith, and J. M. Ballingall, "A 0.15  $\mu\text{m}$  gate-length pseudomorphic HEMT," *IEEE MTT-S Dig.*, pp. 983-986, 1989.

- [4] P. C. Chao, P. M. Smith, K. H. G. Duh, and J. M. Ballingall, "V- and W-band power and low-noise HEMTs," in *Proc. Ext. Abstr. 21st Conf. Solid State Dev. Mat.*, Tokyo, 1989, pp. 277-280.

- [5] P. M. Smith, P. C. Chao, J. M. Ballingall, and A. W. Swanson, "Microwave and mm-wave power application using pseudomorphic HEMTs," *Microwave J.*, pp. 71-86, May 1990.

- [6] T. H. Chen, K. L. Tan, G. S. Dow, H. Wang, K. W. Chang, T. N. Ton, B. Allen, J. Berenz, P. H. Liu, D. Streit, and G. Hayashibara, "A 0.1-W W-band pseudomorphic HEMT MMIC power amplifier," *GaAs IC Symp. Dig.*, pp. 71-74, 1992.

- [7] K. L. Tan *et al.*, "94 GHz 0.1  $\mu\text{m}$  T-gate low noise pseudomorphic InGaAs HEMTs," *IEEE Electron. Device Lett.*, vol. 11, pp. 585-587, 1990.

- [8] H. Wang, T. N. Ton, K. L. Tan, D. Garske, G. S. Dow, J. Berenz, M. W. Pospieszalski, and S. K. Pan, "A D-band monolithic low noise amplifier," *GaAs IC Symp. Dig.*, pp. 23-26, 1992.

- [9] S. Shanfield, A. Platzker, L. Aucoin, T. Kazior, B. I. Patel, A. Bertrand, W. Hoke, and P. Lyman, "One Watt, very high efficiency, 10 and 18 GHz pseudomorphic HEMTs fabricated by dry first recess etching," *IEEE MTT-S Dig.*, pp. 639-641, 1992.

- [10] J. C. Huang, G. Jackson, S. Shanfield, W. Hoke, P. Lyman, D. Atwood, P. Saledas, M. Schindler, Y. Tajimaa, A. Platzker, D. Massé, and H. Staz, "An AlGaAs/InGaAs pseudomorphic high electron mobility transistor (PHEMT) for x- and ku-band power applications," *IEEE MTT-S Dig.*, pp. 713-716, 1991.

- [11] C. S. Wu *et al.*, "High breakdown voltage power PHEMT devices processed with single gate recess and damage-free RIE techniques," to be published.

- [12] A. Kurdoghlian, C. S. Wu, W. Yau, J. Chen, M. Hu, C. K. Pao, and D. Bosch, "The demonstration of Ka-band multi-functional MMIC circuits fabricated on the same PHEMT wafer with superior performance," in *IEEE Dig. Microwave & MM-Wave Monolithic Circ.*, pp. 97-98, 1993.

- [13] C. S. Wu, G. L. Lan, C. K. Pao, S. X. Bar, and M. Hu, "Pseudomorphic HEMT devices for microwave and millimeter wave applications," published in *Proc. MRS Symp.*, 1993, vol. 300, pp. 41-54.

- [14] C. S. Wu, M. Hu, S. X. Bar, C. K. Pao, H. Kanber, B. M. Paine, and W. Yau, "High yield pseudomorphic HEMT manufacturing technology development," in *Proc. 1993 U.S. Conf. GaAs Mfg. Technol.*, 1993, pp. 41-42.

- [15] R. Plana *et al.*, "Noise in AlGaAs/InGaAs/GaAs pseudomorphic HEMT's from 10 Hz to 18 GHz," *IEEE Electron Device Lett.*, vol. 40, no. 5, May 1993.

- [16] C. S. Wu, K. K. Yu, M. Hu, and H. Kanber, "Optimization of Ohmic Contacts for Reliable Heterostructure GaAs Materials," *J. Electronic Materials*, vol. 19, pp. 1265-1271, 1990.

**Chan Shin Wu** (M'88-SM'93) received his M.S. degree in physics from the National Tsing Hua University, Taiwan in 1976 and his Ph.D. degree in electrical engineering from the University of California at San Diego in 1984.

After he obtained his Ph.D. degree, he joined AT&T Bell Laboratories at Murray Hill, where he was a member of the technical staff responsible for the research and development of self-aligned refractory gate GaAs MESFET and HEMT devices and processing for high-speed digital circuits. He was the project leader for the DARPA GaAs pilot line program. In December 1987, he joined GaAs Operations, Hughes Aircraft Company, where he is currently a section head in charge of the research and development of advanced heterojunction microwave and optical devices and processes. He has served as the project leader and principal investigator of various R&D programs on advanced heterojunction devices and components. His work has led to high performance, high yield, microwave/millimeter wave pseudomorphic HEMT (PHEMT) devices and MMIC's, power heterojunction bipolar transistor (HBT) devices, and state-of-the-art performance high radiation hard GaAs based MQW LWIR detectors. He is currently leading the power PHEMT and HBT devices and MMIC technology development.

Dr. Wu has published more than 50 technical papers on semiconductor devices, processing and circuits and holds seven patents. He is a member of the Böhmische Physical Society, Materials Research Society and SPIE.

**C. K. Pao** (S'75-M'76-S'80-S'82-M'82-M'85) received his M.S. degree from the National Chiao Tung University, Taiwan in 1976 and Ph.D. degree from the University of Michigan in 1976, both in electrical engineering.

Dr. Pao has more than nine years of experience in the field of GaAs monolithic microwave integrated circuits. Since joining Hughes in 1985, he has been involved in the development of millimeter wave IMPATT diodes. He developed various MMIC circuits, including, phase shifter, V-band power amplifiers, W-band mixers, and low noise amplifiers. Currently, he is heavily involved in the development of heterojunction device technology including HEMT's and HBT's for both GaAs- and InP-based materials. He is also responsible for the establishment of MMIC cell library and design methodology for MMIC's. He is currently a project engineer.

**W. Yau**, photograph and biography unavailable at time of publication.

**Hilda Kanber** (S'74-M'80-S'80-M'81) received the B.A. degree in Physics from Occidental College and the M.S. and Ph.D. degrees in electrical engineering from the University of Southern California. Between 1975 and 1979, she worked at the Jet Propulsion Laboratory investigating acoustic levitation and containerless processing technology. In 1979 she joined Hughes Aircraft Company and has served in a number of technical and program management positions. She is currently project manager for various programs in the microwave and millimeter-wave IC areas, including task leadership for PHEMT development in the ARPA MIMIC Phase 2 program. During her 15 years at Hughes, her work has involved ion implantation in GaAs and III-V materials, novel techniques for material characterization, MOCVD growth, selective area epitaxy, monolithic microwave devices and IC's, and PHEMT development.

Dr. Kanber has published more than 60 technical papers and holds four patents. She has co-organized and co-chaired various conferences and workshops. She is a member of the American Physical Society, Materials Research Society, and the Electrochemical Society.

**Ming Hu** received the B.S. degree from the National Taiwan University and the Ph.D. degree in chemistry from the University of Southern California, Los Angeles.

She has worked in the area of GaAs material epitaxy growth and characterization, the processing of GaAs pseudomorphic high electron mobility transistor (PHEMT), and heterojunction bipolar transistor (HBT). Currently, she is working on InP power HEMT at Hughes Research Laboratories.

**S. X. Bar**, photograph and biography unavailable at time of publication.

**A. Kurdoghlian**, photograph and biography unavailable at time of publication.

**Zaher Bardai** (M'80) received the B.S. degree (1968) and the Ph.D. degree (1974) from the University of Edinburgh, Edinburgh, Scotland.

He has been with Hughes Aircraft Company since 1985. He is currently the ARPA MIMIC Program Manager and the Manager of the Wireless Telecommunications Business Development Unit at Hughes Microelectronics in Torrance, California. Prior to joining Hughes, he was a Senior Scientist at TRW for five years and worked in several small/start-up companies in California for several years prior to

that. His interests have included magnetostatic-wave devices and circuits, field emitting arrays, silicon power bi-polar technology, and microwave and millimeter-wave circuits in GaAs and related III-V compounds.

He is the author of nine papers and holds six patents.

**Charles Seashore** (M'57) received the B.S. and M.S. degree in electrical engineering and completed course work towards the Ph.D. After serving as an army ordinance officer, he joined Honeywell in 1961 and has served in a number of technical and engineering management positions. He currently is a principal Program Manager at Alliant Techsystems directing programs on MMIC technology, as well as signal processing and LADAR *R* and *D* contracts. He has served as the MIMIC Program Manager for the past seven years. He has served as a guest lecturer at Georgia Tech University and several government agencies on millimeter-wave technology. He is the founder and a past chairman of the MTT Twin Cities Chapter. He is also past chairman of the Communications Technology Twin Cities Chapter.

**Donald Bosch** received the B.S. degree in electrical engineering from North Dakota State University in 1981. From 1981 to 1983 he was employed by the E. F. Johnson company working on SSB transceiver design for telephone service in commercial aircraft. Since 1984 he has been a member of the engineering department at Honeywell and Alliant Techsystems working on MMIC design and development for defense system applications at both microwave and millimeter-wave frequencies.

**Michael Gawronski** (S'70-M'75) received the B.S. and M.S. degree in electrical engineering from Marquette University and the M.B.A. degree from Mankato State University. From 1972 to 1979 he was a member of the technical staff at Westinghouse working on microwave and millimeter-wave receiver protector devices. Since 1979 he has been in the engineering department at Honeywell and Alliant Techsystems, where he is currently engineering manager for millimeter-wave subsystems utilizing hybrid and MMIC technologies. He is chairman of the MTT Twin Cities Chapter and a member of Tau Beta Pi and Eta Kappa Nu.